重大共性工艺-应力工程

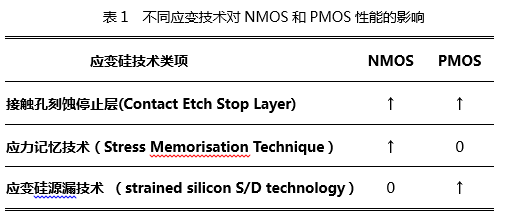

随着COMS工艺的关键尺寸以及栅极氧化层不断缩小(xiǎo),会导致载流子的迁移率大大降低,从而引起器件开态電(diàn)流的降低,器件性能(néng)的退化。应力工程已成為(wèi)12英寸工艺中改善器件性能(néng)的必要技术之一。对于65nm及以下技术代,采用(yòng)的应力工程主要包括:接触孔刻蚀停止层(contact etch stop layer,CESL)、应力记忆技术(Stress Memorization Technique,SMT)和应变硅源漏技术(strained silicon S/D technology) 。

CESL技术通常以PECVD沉积氮化硅為(wèi)主,以SiH4、N2与He混合气體(tǐ)沉积于550~600°C,调整气體(tǐ)流量比、沉积压力与等离子體(tǐ)发射功率等相关参数可(kě)得相对伸张或压缩应力的氮化硅膜,从而增加NMOS和PMOS的载流子迁移率,提高器件性能(néng)。其技术难点有(yǒu)单轴CESL工艺、多(duō)轴CESL工艺和侧墙优化等。

SMT技术主要在NMOS中利用(yòng)Si的氮化物(wù)的盖帽层映入单轴拉应力,从而有(yǒu)效提高電(diàn)子输运性能(néng)。这种方法主要包括以下几个步骤:多(duō)晶硅无定型化,沉积具有(yǒu)拉伸应力的衬层,快速退火,衬层移除。虽然拉伸层移除,但是通过退火过程,应力被记忆下来,从而移除衬层之后沟道仍保留应力。

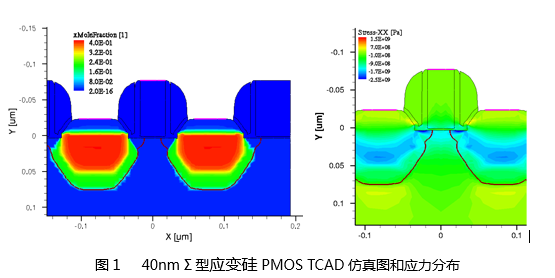

应变硅源漏技术是40nm及以下技术代提高PMOS器件性能(néng)的必备技术。它是通过在沟道中产生单轴压应力来增加PMOS的空穴迁移率,从而提高晶體(tǐ)管的電(diàn)流驱动能(néng)力。应变硅源漏工艺过程复杂,且各个工艺参数互相影响,需要同时满足包括:掺杂浓度,位错缺陷,颗粒缺陷,形貌要求等。

在40nm 技术代,已成功开发了具有(yǒu)应变硅源漏的PMOS器件的TCAD 工艺模型和器件模型,并在大生产線(xiàn)上的40nm PMOS器件进行实验验证了模型的适用(yòng)性和正确性。同时,开发和优化了具有(yǒu)U型和Σ型的应变硅源漏技术方案,成功得到具有(yǒu)应变硅源漏的PMOS器件,其電(diàn)學(xué)性能(néng)达到业界水平。并且对图形片上原位B掺杂应变硅薄膜生長(cháng)机理(lǐ)缺陷机理(lǐ)进行了深入研究和分(fēn)析。

对于28nm技术代的CESL技术、SMT技术和应变硅源漏技术研发也获得了支持。